Rev. J1.4

64M BITS 低消費電力SRAM (4Mx16 / 8Mx8 )

### 改訂記録

| 改訂番号      | 改訂内容                                                                                 | 発行年月日      |

|-----------|--------------------------------------------------------------------------------------|------------|

| Rev. J1.0 | 初版                                                                                   | 2016年4月6日  |

| Rev. J1.1 | 8ページのライトサイクルの下記注意事項1を削除                                                              | 2016年6月28日 |

|           | 1. WE#,CE#, LB#, UB# must be high or CE2 must be low during all address transitions. |            |

| Rev. J1.2 | DC電気的特性、データ保持特性、製品ファミリーと特徴の $I_{ m cc}$ / $I_{ m cc_1}$ /                            | 2017年4月7日  |

|           | I <sub>SB1</sub> (MAX.) /I <sub>DR</sub> (MAX.) を変更                                  |            |

| Rev. J1.3 | 真理値表注意事項追加                                                                           | 2017年5月22日 |

|           | 2. 4M x 16として使う場合はBYTE#は「H」。8M x 8として使う場合にはBYTE#は「L」、ピン45をA-1                        | ٤          |

|           | 使いUB#とLB#は                                                                           |            |

|           | 「L」でDQ8 ~ DQ14は使用しない。                                                                |            |

| Rev. J1.4 | ページ 7と8のライト・サイクルのタイミング波形の部分の誤記訂正                                                     | 2020年7月30日 |

### **REVISION HISTORY**

| <b>Revision</b> | Description                                                                                                      | Issue Date  |

|-----------------|------------------------------------------------------------------------------------------------------------------|-------------|

| Rev. 1.0        | Initial Issue                                                                                                    | Apr.06.2016 |

| Rev. 1.1        | Deleted WRITE CYCLE Notes:                                                                                       | Jun.28.2016 |

|                 | 1. WE#,CE#, LB#, UB# must be high or CE2 must be low during all address transitions. in page 8                   |             |

| Rev. 1.2        | Revised Icc / Icc1 / Isb1(MAX.) /IDR(MAX.) in DC ELECTRICAL                                                      | Apr.07.2017 |

|                 | <b>CHARACTERISTICS &amp; DATA RETENTION CHARACTERISTICS 8</b>                                                    | <b>L</b>    |

|                 | PRODUCT FAMILY & FEATURES                                                                                        |             |

| Rev. 1.3        | Added TRUTH TABLE Notes:                                                                                         | May.22.2017 |

|                 | 2. The BYTE# pin has to be tied to Vcc to use the device as a 4M x 16 SRAM, and to be tied to Vss                | -           |

|                 | as a 8M x 8 SRAM. In the 8M x 8 configuration, Pin 45 is A-1, and both UB# and LB# are tied to $V_{\text{SS}}$ , |             |

|                 | while DQ8 to DQ14 pins are not used.                                                                             |             |

| Rev. 1.4        | Revised typo in <b>TIMING WAVEFORMS</b> of <b>WRITE CYCLE</b> in page 7 & 8                                      | Jul.30.2020 |

64M BITS 低消費電力SRAM (4Mx16 / 8Mx8 )

Rev. J1.4

#### 特長

■ アクセス時間: 55ns (max.)

■ 低消費電力:

動作電流: 12mA (typ.)

スタンバイ電流: 12μA (typ.) SL-グレイト

■ 単一電源動作: 2.7V~3.6V

■ 入出力TTLコンパチブル

■ 完全スタティック動作

■ トライ・ステート出力

■ データ・バイト制御:

(i) BYTE#は「H」 LB#はDQO ~ DQ7制御

UB#はDQ8 ~ DQ15制御

(ii) BYTE#は「L」

DQ15はアドレス入力として使用。

DQ8 ~ DQ 14は使用しない。

■ データ保持最低電源電圧 : 1.2V (min.)

■ グリーン・パッケージ対応

■ パッケージ: 48ピン 12mm x 20mm TSOP I

### 概要

LY62L409816Bシリーズは67,108,864ビットで4,194,304x16ビットと8,388,608x8ビットの切り替え可能な低消費電力CMOSスタティックRAMです。

高性能と高信頼性CMOS技術を採用し全動作温度範囲において安定したスタンバイ電流特性を持っています。

LY62L409816Bシリーズは低消費電力の商品に適しています。特に電源切断時に二次電源でバックアップしデータを保持する必要のあるシステムに最適です。

LY62L409816Bシリーズは単一の2.7V  $^{\sim}$  3.6Vの電源で動作し全ての入出力はTTLコンパチです。

### 製品ラインナップ

| Product         | Operating   | Voc Pango                      | Spood | Power Dissipation               |                                  |  |  |

|-----------------|-------------|--------------------------------|-------|---------------------------------|----------------------------------|--|--|

| Family          | Temperature | V <sub>CC</sub> Range Speed St |       | Standby(I <sub>SB1</sub> ,TYP.) | Operating(I <sub>CC</sub> ,TYP.) |  |  |

| LY62L409816A    | 0 ~ 70℃     | 2.7 ~ 3.6V                     | 55ns  | 12μA(SL)                        | 12mA                             |  |  |

| LY62L409816A(I) | -40 ~ 85°C  | 2.7 ~ 3.6V                     | 55ns  | 12μA(SL)                        | 12mA                             |  |  |

Rev. J1.4 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8 )

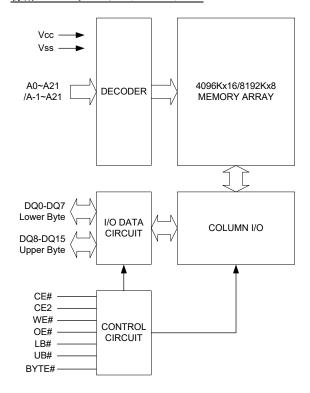

### 機能ブロックダイアグラム

### ピン名称

| SYMBOL     | DESCRIPTION               |

|------------|---------------------------|

| A0 - A21   | Address Inputs(word mode) |

| A-1 - A21  | Address Inputs(byte mode) |

| DQ0 - DQ15 | Data Inputs/Outputs       |

| CE#, CE2   | Chip Enable Input         |

| WE#        | Write Enable Input        |

| OE#        | Output Enable Input       |

| LB#        | Lower Byte Control        |

| UB#        | Upper Byte Control        |

| BYTE#      | Byte Enable               |

| Vcc        | Power Supply              |

| Vss        | Ground                    |

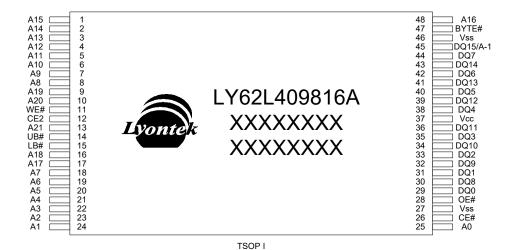

### ピン配置

**Lyontek Inc.** reserves the rights to change the specifications and products without notice. 2F, No.17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan.

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

#### 絶対最大定格\*

| PARAMETER                                            | SYMBOL           | RATING                       | UNIT         |

|------------------------------------------------------|------------------|------------------------------|--------------|

| Voltage on $V_{CC}$ relative to $V_{SS}$             | V <sub>T1</sub>  | -0.5 to 4.6                  | V            |

| Voltage on any other pin relative to V <sub>SS</sub> | $V_{T2}$         | -0.5 to V <sub>CC</sub> +0.5 | V            |

| Operating Temperature                                | т                | 0 to 70(C grade)             | $^{\circ}$   |

| Operating Temperature                                | T <sub>A</sub>   | -40 to 85(I grade)           | C            |

| Storage Temperature                                  | T <sub>STG</sub> | -65 to 150                   | $^{\circ}$ C |

| Power Dissipation                                    | P <sub>D</sub>   | 1                            | W            |

| DC Output Current                                    | Іоит             | 50                           | mA           |

<sup>\*「</sup>絶対最大定格」に記載されている以上のストレスは、デバイスに恒久的な損傷を与える可能性があります。これはストレス量のみでありデバイスの機能的な動作や、この仕様の動作セクションに示されている条件を超えるその他の条件を意味するものではありません。長期にわたり絶対最大定格条件に曝すとデバイスの信頼性に影響を与える可能性があります。

### 真理値表 (動作表)

| MODE            | CE# | CE2 | BYTE | OE# | WE# | LB# | UB# | I/O              | SUPPLY           |        |                  |

|-----------------|-----|-----|------|-----|-----|-----|-----|------------------|------------------|--------|------------------|

| MODE            | OL# | OLZ | #    | OL# | *** | LD# | OD# | DQ0-DQ7          | DQ8-DQ14         | DQ15   | CURRENT          |

| Standb          | Н   | Х   | Х    | Х   | Х   | Х   | Х   | High-Z           | High-Z           | High-Z |                  |

|                 | Χ   | L   | Х    | Χ   | Х   | Χ   | X   | High-Z           | High-Z           | High-Z | I <sub>SB1</sub> |

| У               | Χ   | X   | Н    | X   | Χ   | Н   | Н   | High-Z           | High-Z           | High-Z |                  |

| Output          | L   | Н   | Н    | Н   | Н   | L   | Х   | High-Z           | High-Z           | High-Z |                  |

| Disable         | L   | Н   | Н    | Н   | Н   | Χ   | L   | High-Z           | High-Z           | High-Z | Icc,Icc1         |

| Disable         | L   | Н   | L    | Н   | Н   | L   | L   | High-Z           | High-Z           | A-1    |                  |

|                 | L   | Н   | Н    | L   | Н   | L   | Н   | Dout             | High-Z           | High-Z |                  |

| Read            | L   | Н   | Н    | L   | Н   | Н   | L   | High-Z           | D <sub>оит</sub> | Dout   | Icc,Icc1         |

|                 | L   | Н   | Н    | L   | Н   | L   | L   | D <sub>оит</sub> | D <sub>оит</sub> | Dout   |                  |

|                 | L   | Н   | Н    | Χ   | L   | L   | Н   | Din              | High-Z           | High-Z |                  |

| Write           | L   | Н   | Н    | Χ   | L   | Н   | L   | High-Z           | DIN              | DIN    | lcc,lcc1         |

|                 | L   | Н   | Н    | X   | L   | L   | L   | D <sub>IN</sub>  | D <sub>IN</sub>  | $D_IN$ |                  |

| Byte#<br>Read   | L   | Н   | L    | L   | Н   | L   | L   | D <sub>оит</sub> | High-Z           | A-1    | Icc,Icc1         |

| Byte #<br>Write | L   | Н   | L    | Х   | L   | L   | L   | Din              | High-Z           | A-1    | Icc,Icc1         |

#### 注意事項

<sup>1. 「</sup>H」はハイレベル入力、「L」はローレベル入力。「X」は「H」又は「L」レベルのどちらでも良い。

<sup>2. 4</sup>M x 16として使う場合はBYTE#は「H」。8M x 8として使う場合にはBYTE#は「L」、ピン45をA-1として使いUB#とLB#は「L」でDQ8  $^{\circ}$  DQ14は使用しない。

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

#### DC 電気的特性

| PARAMETER                 | SYMBOL             | TEST CONDITION                                                                                          | N                         | MIN.  | TYP. *4 | MAX.    | UNIT |

|---------------------------|--------------------|---------------------------------------------------------------------------------------------------------|---------------------------|-------|---------|---------|------|

| Supply Voltage            | Vcc                |                                                                                                         |                           | 2.7   | 3.0     | 3.6     | V    |

| Input High Voltage        | $V_{IH}^{*1}$      |                                                                                                         |                           | 2.2   | ı       | Vcc+0.3 | V    |

| Input Low Voltage         | V <sub>IL</sub> *2 |                                                                                                         |                           | - 0.2 | ı       | 0.6     | V    |

| Input Leakage Current     | ILI                | $V_{CC} \ge V_{IN} \ge V_{SS}$                                                                          |                           | - 1   | -       | 1       | μA   |

| Output Leakage<br>Current | ILO                | cc ≧ Vouт ≧ Vss<br>utput Disabled                                                                       |                           | - 1   | -       | 1       | μA   |

| Output High Voltage       | Vон                | I <sub>OH</sub> = -1mA                                                                                  | <sub>рн</sub> = -1mA      |       |         | -       | V    |

| Output Low Voltage        | Vol                | I <sub>OL</sub> = 2mA                                                                                   | oL = 2mA                  |       |         | 0.4     | V    |

| Average Operating         | lcc                | $I_{I/O} = 0mA$                                                                                         | CE#≦0.2V and CE2≧Vcc-0.2V |       | 12      | 20      | mA   |

| Power supply Current      | lcc <sub>1</sub>   | Cycle time = 1µs<br>CE#≦0.2V and CE2≧Vcc-0.2V<br><sub>I/O</sub> = 0mA<br>Other pins at 0.2V or Vcc-0.2V |                           | -     | 3       | 5       | mA   |

|                           |                    | CE#≧Vcc-0.2V                                                                                            | ·SL *5 25℃                | -     | 12      | 32      | μA   |

| Standby Power             | las.               |                                                                                                         | ·SLI *5 40°C              | -     | 12      | 36      | μA   |

| Supply Current            | I <sub>SB1</sub>   |                                                                                                         | SL (70°C)                 | -     | -       | 100     | μA   |

|                           |                    | or Vcc-0.2V                                                                                             | -SLI (85℃)                | -     | -       | 160     | μA   |

#### 注意事項

- \*1. 最大入力電圧、 $V_{\text{IH}}$  (max.) は 6ns 以内のパルス幅で  $V_{\text{CC}}$  + 2.0V とする。

- \*2. 最低入力電圧、 $V_{\text{IL}}$  (min.)は 6ns 以内のパルス幅で  $V_{\text{SS}}$  2.0V とする。

- \*3. オーバー/アンダーシュートに関しては製品評価段階で評価済みですが、量産時のテストはしていません。

- \*5. この項目はVcc=3.0Vにおける参考値。

### 負荷容量 (T<sub>A</sub>=25℃, f=1.0MHz)

| PARAMETER                | SYMBOL           | MIN. | MAX. | UNIT |

|--------------------------|------------------|------|------|------|

| Input Capacitance        | Cin              | -    | 15   | pF   |

| Input/Output Capacitance | C <sub>I/O</sub> | -    | 20   | pF   |

注意事項:これらのパラメータは製品評価で保証されていますが、量産時のテストはしていません。

2F, No.17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan.

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8 )

### AC テスト条件

| Input Pulse Levels                       | 0.2V to V <sub>CC</sub> - 0.2V                   |

|------------------------------------------|--------------------------------------------------|

| Input Rise and Fall Times                | 3ns                                              |

| Input and Output Timing Reference Levels | 1.5V                                             |

| Output Load                              | $C_L = 30pF + 1TTL$ , $I_{OH}/I_{OL} = -1mA/2mA$ |

### AC 電気的特性

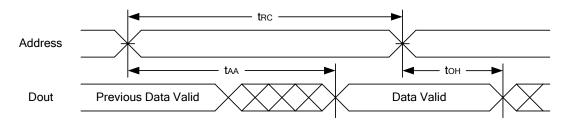

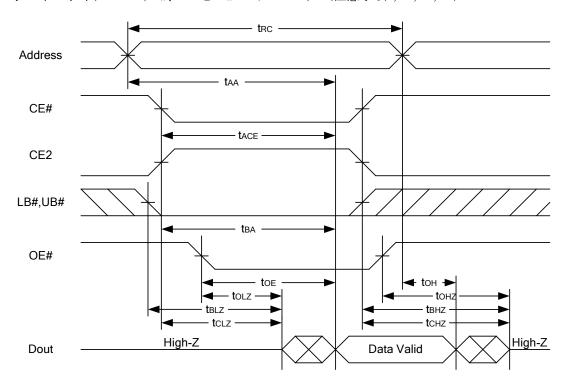

#### (1) リード・サイクル

| PARAMETER                          | SYM.               | LY62L409 | UNIT |      |

|------------------------------------|--------------------|----------|------|------|

| PARAMETER                          | STIVI.             | MIN.     | MAX. | UNII |

| Read Cycle Time                    | t <sub>RC</sub>    | 55       | -    | ns   |

| Address Access Time                | taa                | -        | 55   | ns   |

| Chip Enable Access Time            | <b>t</b> ACE       | -        | 55   | ns   |

| Output Enable Access Time          | toe                | -        | 30   | ns   |

| Chip Enable to Output in Low-Z     | tcLz*              | 10       | -    | ns   |

| Output Enable to Output in Low-Z   | t <sub>OLZ</sub> * | 5        | -    | ns   |

| Chip Disable to Output in High-Z   | t <sub>CHZ</sub> * | -        | 20   | ns   |

| Output Disable to Output in High-Z | tonz*              | -        | 20   | ns   |

| Output Hold from Address Change    | toh                | 10       | -    | ns   |

| LB#, UB# Access Time               | <b>t</b> BA        | -        | 55   | ns   |

| LB#, UB# to High-Z Output          | t <sub>BHZ</sub> * | -        | 20   | ns   |

| LB#, UB# to Low-Z Output           | t <sub>BLZ</sub> * | 10       | -    | ns   |

#### (2) ライト・サイクル

| PARAMETER                        | SYM.            | LY62L409 | UNIT |      |

|----------------------------------|-----------------|----------|------|------|

| PARAMETER                        | STIVI.          | MIN.     | MAX. | UNII |

| Write Cycle Time                 | twc             | 55       | -    | ns   |

| Address Valid to End of Write    | t <sub>AW</sub> | 50       | -    | ns   |

| Chip Enable to End of Write      | tcw             | 50       | -    | ns   |

| Address Set-up Time              | t <sub>AS</sub> | 0        | -    | ns   |

| Write Pulse Width                | twp             | 45       | -    | ns   |

| Write Recovery Time              | twr             | 0        | -    | ns   |

| Data to Write Time Overlap       | t <sub>DW</sub> | 25       | -    | ns   |

| Data Hold from End of Write Time | t <sub>DH</sub> | 0        | -    | ns   |

| Output Active from End of Write  | tow*            | 5        | -    | ns   |

| Write to Output in High-Z        | twHz*           | -        | 20   | ns   |

| LB#, UB# Valid to End of Write   | t <sub>BW</sub> | 50       | -    | ns   |

<sup>\*</sup>各パラメータは製品特性上の保証値ですが、量産時のテストはしていません。

Rev. J1.4

### 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

#### タイミング波形

リード・サイクル1 (アドレス・コントロール) (注意事項1, 2)

リード・サイクル2 (CE#、CE2とOE# ントロール) (注意事項1, 3, 4, 5)

#### 注意事項

- 1. リード・サイクル時には WE#はハイレベルでなければなりません。

- 2.0E#と CE#はローレベル、CE2 はハイレベル、LB#と UB#のどちらかでもローレベルの場合はリード・サイクルとなります。

- 3. アドレスは CE#はローレベル、CE2 =ハイ、LB#または UB#はローレベルに変化する前、または同時に有効でなければなりません。もしそうでなければ  $t_{\rm Al}$  は保証されません。

- $4.~t_{CLZ}$ 、 $t_{BLZ}$ 、 $t_{OLZ}$ 、 $t_{CHZ}$ 、 $t_{BHZ}$ 、および  $t_{OHZ}$ は、CL=5pF で指定されます。 その変化は定常状態から $\pm500mV$  の測定です。

- 5. 温度および電圧が同じ条件であればtcHzはtcLzより小さく、tBHzはtBLzより小さく、tOHzはtOLzより小さくなります。

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

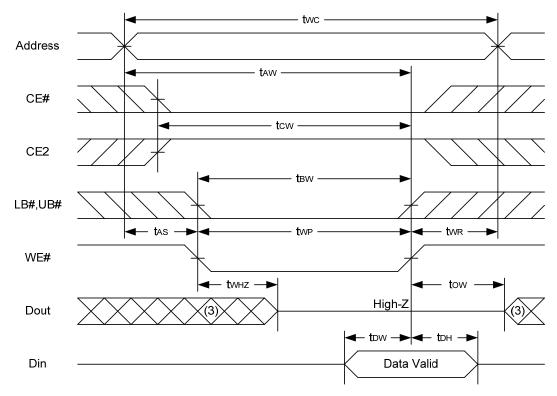

**ライト・サイクル1** (WE# コントロール) (注意事項 1, 2, 4, 5)

**ライト・サイクル 2** (CE#とCE2 コントロール) (注意事項 1,4,5)

**Lyontek Inc.** reserves the rights to change the specifications and products without notice.

2F, No.17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan.

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

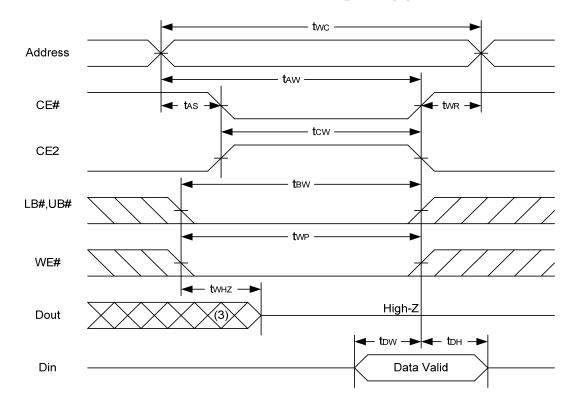

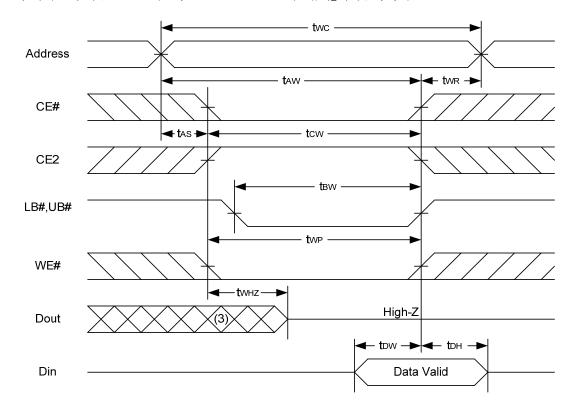

#### **ライト・サイクル 3** (LB#, UB# コントロール) (注意事項 1, 4, 5)

#### 注意事項

- 1. 書き込みはCE#は $u-\nu$ ベル、CE2はハイレベル、WE#はハイレベル、LB#またはUB#は $u-\nu$ ベルのオーバーラップ中に実行されます。

- 2.0E#がローレベルのWE#制御書き込みサイクル中、内部回路のドライバーをオフにしてデータを書き込みするには $t_{PP}$ を $t_{WEZ}$  +  $t_{DW}$ より大きくする必要があります。

- 3. この期間、I/0ピンは出力状態にあり入力信号を印加してはいけません。

- 4. CE#、LB#、UB#のローレベルへの変化およびCE2のハイレベルへの変化がWE#のローレベルへの変化と同時にまたはその後に発生した場合、出力は高インピーダンス状態になります。

- 5. towおよびtwizはCL = 5pFの条件です。 この変化は定常状態から±500mVでの測定です。

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

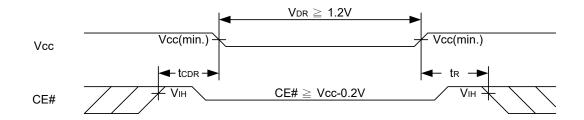

### データ保持特性

| PARAMETER                              | SYMBOL         | TEST CONDITION                                                                                          |      |             | MIN.             | TYP. | MAX. | UNIT |

|----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------|------|-------------|------------------|------|------|------|

| Vcc for Data Retention                 | $V_{DR}$       | CE#≧V <sub>CC</sub> - 0.2V or CE2≦0.2V                                                                  |      |             | 1.2              | -    | 3.6  | V    |

| Data Retention Current                 |                | \\\-\-\-\-\-\-\-\\\\\\\\\\\\\\\\\\\\\\                                                                  | -SL  | <b>25</b> ℃ | -                | 10   | 32   | μΑ   |

|                                        | IDR            | $V_{CC}$ = 1.2V<br>CE# $\geq$ $V_{CC}$ -0.2V or CE2 $\leq$ 0.2V<br>Other pins at 0.2V or $V_{CC}$ -0.2V | -SLI | 40℃         | -                | 10   | 36   | μA   |

|                                        | IDK            |                                                                                                         | -SL  |             | -                | -    | 100  | μA   |

|                                        |                | Out of pind at 0.2 v of vee 0.2 v                                                                       |      |             | -                | -    | 160  | μA   |

| Chip Disable to Data<br>Retention Time | tcdr           | See Data Retention Waveforms (below)                                                                    |      |             | 0                | -    | -    | Ns   |

| Recovery Time                          | t <sub>R</sub> |                                                                                                         |      |             | t <sub>RC*</sub> | -    | -    | Ns   |

t<sub>RC\*</sub> = Read Cycle Time

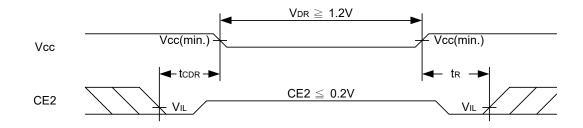

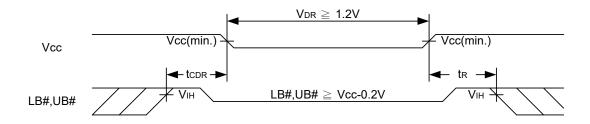

### データ保持タイミング・チャート

データ保持タイミング・チャート 1 (CE# コントロール)

データ保持タイミング・チャート 2 (CE2 コントロール)

データ保持タイミング・チャート 3 (LB#、UB# コントロール)

Lyontek Inc. reserves the rights to change the specifications and products without notice.

2F, No.17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan.

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8)

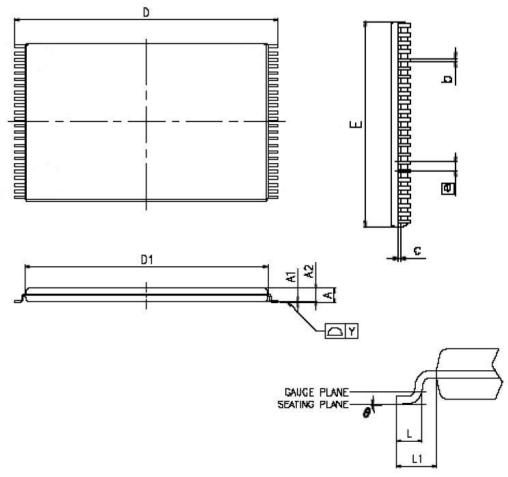

#### \_\_ パッケージ外形寸法

48ピン 12mm x 20mm TSOP I パッケージ外形寸法

#### VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

|   | ANAMINIA OUT NWITHOUTS SHOWN IN MM) |            |           |       |  |  |  |

|---|-------------------------------------|------------|-----------|-------|--|--|--|

|   | SYMBOLS                             | MIN.       | NOM.      | MAX   |  |  |  |

|   | A                                   | ı          | ı         | 1.20  |  |  |  |

|   | A1                                  | 0.05 -     |           | 0.15  |  |  |  |

|   | A2                                  | 0.95       | 0.95 1.00 |       |  |  |  |

|   | ь                                   | 0.17       | 0.22      | 0.27  |  |  |  |

|   | С                                   | 0.10       | ı         | 0.21  |  |  |  |

| Δ |                                     | 19.80      | 20.00     | 20.20 |  |  |  |

| Δ | □1                                  | 18.30      | 18.40     | 18.50 |  |  |  |

| Δ | Е                                   | 11.90      | 12.00     | 12.10 |  |  |  |

|   | €                                   | 0.50 BASIC |           |       |  |  |  |

|   | L                                   | 0.50       | 0.60      | 0.70  |  |  |  |

| Δ | L1                                  | ı          | 0.80      | ı     |  |  |  |

| Λ | Υ                                   |            | -         | 0.10  |  |  |  |

| Δ | θ                                   | Ġ          | _         | 5     |  |  |  |

#### NOTES:

- 1 JEDEC OUTLINE : MO-142 DD

- 2.PROFILE TOLERANCE ZONES FOR D1 AND E DD NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION ON E IS 0.15 mm PER SIDE AND ON D1 IS 0.25 mm PER SIDE.

- 3.D MENSION & DOES NOT INCLUDE DAMBAR PROTRUSION ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE & DIMENSION AT NAXIMUN MATERIAL CONDITION DAMBAR CANNOT BE LOCATED ON THE LOWIER RADIUS OR THE FOOT.

Lyontek Inc. reserves the rights to change the specifications and products without notice.

2F, No.17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan.

Rev. J1.4

## 64M BITS 低消費電力SRAM (4Mx16 / 8Mx8 )

### 注文時の関連情報

| Package Type            | Access Time | Power Type | Temperature | Packing   | Lyontek Item No.      |

|-------------------------|-------------|------------|-------------|-----------|-----------------------|

|                         | (Speed)(ns) |            | Range(°ℂ)   | Type      |                       |

| 48-pin                  | 55          | Low Power  | 0°C~70°C    | Tray      | LY62L409816ALL-55SL   |

| (12mm x 20mm)<br>TSOP I |             |            |             | Tape Reel | LY62L409816ALL-55SLT  |

| 1001 1                  |             |            | -40°C~85°C  | Tray      | LY62L409816ALL-55SLI  |

|                         |             |            |             | Tape Reel | LY62L409816ALL-55SLIT |